что такое тактовый генератор

Собираем 8-битный компьютер

У меня нет цели научить читателя компьютерной электронике, но есть цель немного о ней рассказать и заинтересовать для самостоятельного изучения. Поэтому в статье упущено много базовой информации, нет деталей реализации различных компонентов, упрощены схемы — я не хочу перегружать материал. Если вас заинтересует статья, в конце есть раздел со всеми ссылками на видео и книгу для детального ознакомления.

Видеоиллюстрация

На видео снизу я разбираю программу для вывода на экран чисел Фибоначчи, написанную на языке C. Из кода на языке С, я генерирую код на языке ассемблера, чтобы лучше понять принципы выполнение программы на компьютере. Так как компьютер из статьи не понимает язык ассемблера, я перевожу его на язык, который он понимает.

Вы можете посмотреть первые 10 секунд видео, в котором демонстрируется выполнение программы, вернуться на статью и дочитать ее, а потом с бóльшим контекстом досмотреть видео.

Архитектура

Компьютер построен на архитектуре SAP-1 simpleaspossible. SAP-1 — это архитектура для начинающих, главная цель — понять базовые идеи и концепции построения компьютера без углубления в детали. Дизайн специально разработан для академических целей.

Большинство деталей в проекте — это 7400 серия интегральных микросхем от Texas Instruments, американской компании-производителя полупроводниковых изделий.

Компоненты

Компьютер состоит из следующих компонентов:

Регистр адреса оперативной памяти.

Буферные регистры A и B.

Регистр ввода-вывода и дисплей.

Шина для адреса и данных.

Схема

Схема расположения компонентов выглядит следующим образом:

Компоненты

Тактовый генератор

Тактовый генератор координирует работу всех компонентов в компьютере. Он подключен почти к каждому компоненту отдельно и раз в определенное время выдает напряжение. Это нужно для того, чтобы синхронизировать выполнение программы разными частями компьютера.

В основе тактового генератора лежит чип LM555CN — это таймер, устройство для формирования повторяющихся импульсов тактовых сигналов. С помощью резисторов и конденсатора можно контролировать частоту импульсов. Так, например, у Intel Core i9-7980XE базовая тактовая частота — 2.60 GHz. Это значит, что за одну секунду выдается 2.6 миллиарда импульсов.

Частота импульса складывается из времени наличия напряжения и его отсутствия как проиллюстрировано на рисунке ниже. По формуле ниже, она из документации к таймеру, при резисторе А — 100 Ом, резисторе B — 100K Ом, конденсаторе С — 2 микрофарад, получается, что один такт занимает — 0.693 * 201000 * 0.000002 = 0.278 секунды. За одну секунду получится — 1 / 0.278 = 3.59 такта.

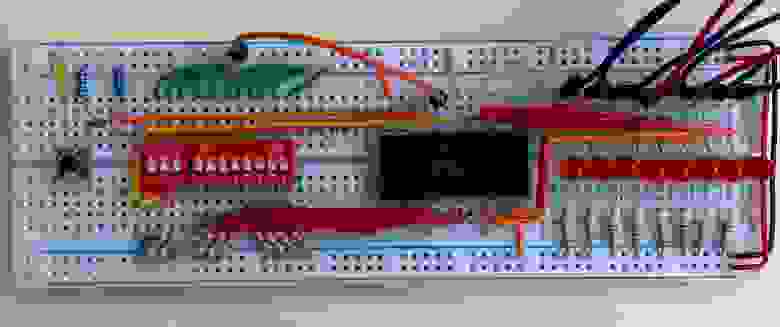

Пример использования тактового генератора — внизу на картинке на макетной плате находится чип SN74LS173, это 4-битный D flip-flop — он нужен для того, чтобы хранить 4 битовых значения. Таким образом можно хранить 16 комбинаций значений, от 0000 до 1111. У чипа 16 ножек с помощью которых он вставляется в плату. Каждая из которых отвечает за свою часть работы. Чтобы не вдаваться в подробности, если на M и N разрешение на запись, и 1D подать напряжение, мы ожидаем, что чип сохранит значение как напряжение и отобразит это в 1Q, выход которого ведет к диоду красная лампочка — но ничего не произойдет. Для сохранения значения нам нужно также подать напряжение на вход CLK clock signal — тактовый сигнал, который исходит из тактового генератора.

В проекте тактовый генератор чуть-чуть сложнее:

Вместо резистора на 100К Ом там находится потенциометр, это «резистор с крутилкой», его можно поворачивать за и против часовой стрелки и динамически изменять сопротивление от 0 ОМ до 1М Ом. Таким образом можно увеличить количество тактов в секунду и компьютер будет работать быстрее, и наоборот.

Вместо одного таймера, там три, переключатель и кнопка. Это позволяет переключаться между двумя режимами — ручной и автоматический. В ручном режиме такт совершается при нажатии кнопки — это позволяет дебагать работу компьютера, а автоматический вы уже видели.

Оперативная память

Оперативная память нужна компьютеру, чтобы хранить определенный набор данных по определенным адресам. Оперативная память используется для хранения команд компьютера (например, сложить два числа), адресов (сложить число по какому-то адресу) и данных (записать какое-то число по какому-то адресу).

Знакомый нам чип SN74LS173 может сохранить 4 бита информации, чтобы сохранить 8 бит информации — нужно взять два SN74LS173. Таким образом, мы можем хранить значения от 0000 0000 до 1111 1111, что равно 256 возможных комбинаций, 2 в степени 8.

На схеме ниже к двум SN74LS173 подключен DIP-переключатель на 8 переключателей, которыми можно задавать 8 бит информации. Так как переключатели подсоединены к питанию, если переключить один из них, он выдаст напряжение. При подаче сигнала от тактового генератора, это значение сохранится в чипе и соответствующий диод загорится.

На самом деле, мы хотим контролировать когда производить запись. Без этого в памяти может оказаться любое значение – например, мы начинаем переключать переключатели, не переключили до конца, а тактовый сигнал сработал и память обновилась.

Для этого мы соединяем входы M и N с кнопкой. Кнопка подключена к напряжению, если на нее нажать, она передаст напряжение по перемычке. Нажав на кнопку и дождавшись тактового сигнала, мы получим запись значения.

Таким образом, схематически, можно выразить масштабируемость оперативной памяти как наличие одной кнопки, которая контролирует запись 8 бит. Если мы хотим иметь 128 бит оперативной памяти, а именно столько памяти в проекте, нам нужно 16 кнопок, каждая из которых отвечает за свои 8 ячеек оперативной памяти 16 * 8 = 128.

Если бы мы горизонтально подключили все ячейки между собой все первые ячейки каждой колонки, все вторые, третьи и так далее, соединив с одним переключателем на 8 переключателей, мы могли бы контролировать в какую именно колонку записать переданное через переключатели значение нажатием кнопки. Нажали на 16-ю кнопку — значение записалось только в последнюю колонку ячеек.

Кнопки получились бы репрезентацией адресов оперативной памяти. Но это сложно масштабировать, легче масштабировать бинарное представление 16 кнопок. То есть 4 бита, от 0000 до 1111 — в сумме 16 комбинаций, что равно количеству кнопок и, соответственно, колонок ячеек. С этим поможет DIP-переключатель на 4 переключателя.

Если значение переключателей будет 0000 — выбираем первый ряд, если 0001 — второй ряд, 0011 — четвертый ряд, и так далее до 1111 — 16 ряд. Раз кнопки превратились в переключатели, а переключатели превратились в перенаправление на определенную колонку ячеек, мы потеряли кнопку на запись — которую тоже надо добавить.

Таким образом, мы изобретаем декодер адресов. На вход декодера подается 4 сигнала, отвечающих за адрес в памяти, и 1 сигнал, отвечающий за запись.

Мы не будем разбирать устройство декодера. Внутри декодера находится комбинационная логика — логические вентили И AND и инверторы NOT. Иллюстрация работы в коротком видео здесь.

Таким образом, мы имеем 4 переключателя для адресов, 8 переключателей для значений ячеек, 1 кнопка на запись значений.

Арифметико-логическое устройство

Арифметико-логическое устройство (АЛУ) — компонент, который выполняет арифметические и логические операции. Например, АЛУ в проекте умеет суммировать и вычитать два числа, каждое из которых представлено 8 битами. Вид операции зависит от положения тумблера: замкнутый тумблер даст сигнал АЛУ сложить числа, разомкнутый вычесть одно число из другого.

Результат операции сразу сохраняется в отдельный 8-битный регистр, чтобы позже выполнить другие функции над ним — например, положить в оперативную память по какому-то из адресов. Этот регистр называется регистр для суммы.

Но на самом деле, АЛУ не принимает произвольные значения из переключателей. Каждое значение хранится в отдельном регистре — A и B. Эти регистры являются буферными регистрами. Буферные регистры предназначены для временного хранения данных и напрямую подключены ко входам АЛУ.

Регистры A и B почти идентичны по строению 4 знакомых нам чипа SN74LS173, но у них разные задачи. Регистр A призван сохранять промежуточный результат вычислений — один операнд, а регистр B призван хранить другой операнд.

Ниже в коде чуть более наглядно о задачах регистров на примере счётчика с инкрементом. Изначально, мы инициализируем переменную a и регистр А значением 0, переменную b регистр B значением 2. Cуммируем a и b, сохраняя в переменную sum регистр суммы в АЛУ. Значение из sum перезаписывается в a. Повторяем в цикле пока a меньше 255.

Схема архитектуры, которую вы уже видели, и пример задачи показывает, что:

Регистр суммы в АЛУ нужен для сохранения результата операции между регистрами A и B — значение можно передать в другие компоненты через шину данных. Например, в регистр A и решить этим задачу с инкрементом.

Регистр B нужен для хранения вспомогательных значений — в него можно только записать через шину данных.

Регистр A нужен для временного хранения значений — его можно передать в другие компоненты через шину данных.

Также АЛУ не подключен к тактовому генератору, это видно на схеме выше, — это ассинхронный компонент. Это значит, что он отрабатывает сразу как только меняются значения в A и/или B. Это достигается за счет того, что в состав АЛУ включены только комбинационные схемы, как у декодера адресов.

Регистр ввода-вывода и дисплей

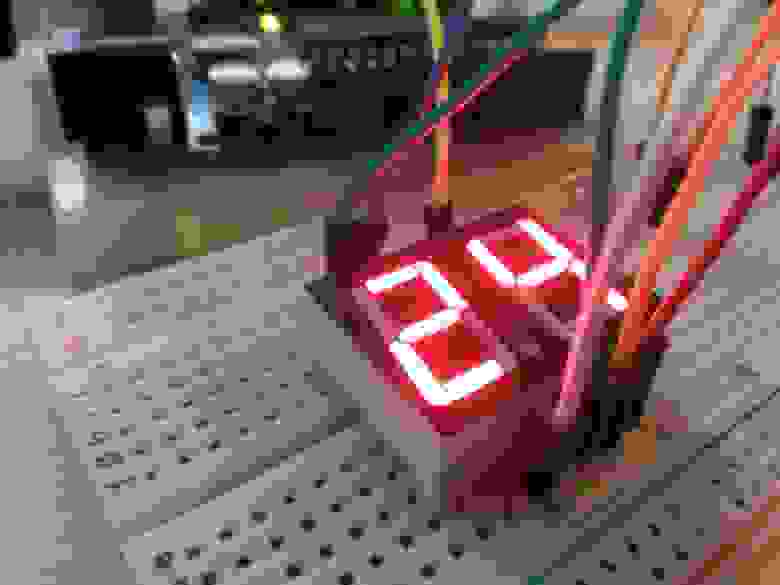

Внизу на картинке изображен семисегментный индикатор — он может отображать цифры и буквы. Он состоит из семи сегментов, включающихся и выключающихся по отдельности — с помощью подачи питания на опредленные ножки.

Чтобы отобразить букву F, нужно подать питание на 1, 2, 4 и 6 ножки слева направо, сверху вниз. Чтобы отобразить цифру 1, нужно подать питание на 5 и 9 ножки. Вместо порядкового номера ножки, можно использовать буквы на схеме — для цифры 1 это B и C.

Если мы хотим отобразить число, состоящее из нескольких цифр, мы можем использовать несколько индикаторов.

В проекте таких индикаторов 3 — они используются для отображения чисел в диапазоне от 0 00000000 до 255 11111111, один индикатор на одно число 0 отображается как 000, 1 как 001. Также в индикаторе есть ножка десятичного знака DP на схеме на случай, если нужно отображать числа с дробной частью (например, 17.3) — но такой функциональности в проекте нет, поэтому эта ножка не используется. Как вы поняли, шестнадцатеричная система счисления в проекте не используется, вместо F (15), используется два дисплея с 1 и 5.

Снизу проиллюстрированы все возможные варианты отображения одного десятичного числа на дисплее.

Теперь нужно понять как «соединить» 4-битное значение в диапазоне от 0000 0 до 1111 9 с входами дисплея от A до G. Например, если значение 0011, то на B и C нужно подать напряжение, а на A, D, E, F, G не нужно. С этим поможет таблица истинности ниже.

Вы могли заметить, что эта таблица похожа на структуру данных ассоциативный массив. Такой массив может хранить пары вида ключ-значение и поддерживает операции добавления пары, поиска и удаления.

Что еще похоже на ассоциативный массив? Оперативная память — адрес на вход и значения на выход. Мы можем сохранять по адресам, которые соответствуют двоичным числам 1001, значения для входов дисплея, которые соответствуют десятичному отображению 9.

Но оперативная память нам не подойдет потому, что не может хранить свои данные «вечно», только при наличии питания. Это значит, что нам придется каждый раз заново записывать в оперативную память значения из таблицы истинности.

Кроме оперативной памяти есть еще другие, которые сохраняют ее свойства (адреса, значения, запись и так далее):

ROM (read-only memory) — на заводе изготовителя «заливают» значения по адресам, а после значения изменить нельзя. Если надо что-то изменить, необходимо менять чип целиком.

PROM (programmable read-only memory) — изготавливается с «чистыми» значениями, которые можно запрограммировать один раз.

EPROM (erasable programmable read-only memory) — память можно перезаписывать, но чтобы стереть значения нужно несколько часов держать специальное окошко на чипе под светом ультрафиолетовой лампы. Окошко заклеивается наклейкой или изолентой.

EEPROM (electrically erasable programmable read-only memory) — память можно перезаписывать сколько угодно раз с помощью электрических импульсов — напряжения.

В проекте используется EEPROM — AT28C16. У него 11 входов для адресов (от 00000000000 до 11111111111) — это 2^11 комбинаций, то есть 2048 адресов и 8 ячеек памяти на каждый адрес. В сумме это память на 16384 бит (2048 байт,

2 килобайта). С помощью входа OE (output enable), подавая напряжение, можно регулировать — выводить ли на выходы I/O то, что хранится в памяти или нет. С помощью входа WE (write enable), подавая напряжение, при «выключенном» OE, можно сделать из выходов I/O входы для записи в ячейки памяти.

Плата, некий пульт управления памятью, с помощью которой можно менять значения в ячейках и смотреть, что хранится по тому или иному адресу, выглядит вот так:

С помощью DIP-переключателей задается адрес, с помощью диодов выводится значение в ячейке. С помощью перемычек (проводков над диодами) задаются новые значения.

Как отобразить число от 0 до 9 на дисплее мы разобрались. Теперь нужно понять как отобразить трехзначное число (например, 123) на 3 дисплеях. Сложность здесь в том, что на регистр ввода-вывода передается одно 8-битное значение (для 255 это 1111011), а на выходе не 1 дисплей, а 3.

Есть много решений этой задачи, в проекте используется сложный, но менее затратный по ресурсам (нужно меньше чипов). О сложном решении рассказать текстом не просто, поэтому обсудим простое решение.

Для каждой цифры из трехзначного числа — свой отдельный дисплей, а для каждого дисплея — свой отдельный EEPROM. Все адреса EEPROM-ов соединены между собой — это значит, что если на вход в регистр ввода-вывода попадет адрес — он попадет на все EEPROM-ы.

Фишка здесь в том, что каждый из EEPROM-в отображает только часть числа. Первый — первую цифру, второй — вторую, третий — третью. Это достигается за счет того, что каждый из них имеет свою таблицу истинности — различную друг от друга.

На каждый из EEPROM-ов приходит адрес 1111011 (число 123). Первый должен отобразить 1 — значит, в ячейке памяти по адресу 1111011 лежит — 0110000 (значения для дисплея). У второго в памяти лежит — 2 (1101101), у третьего — 3 (1111101).

Счётчик команд

В проекте, как и в современных компьютерах, в оперативной памяти хранятся не только значения, но и инструкции. Инструкции — это команды для компьютера сделать то или иное действие.

Оператор компьютера человек заполняет оперативную память инструкциями — одна инструкция в одной ячейке оперативной памяти, а компьютер выполняет эти инструкции одну за одной — для этого ему нужен счётчик команд.

Какие есть инструкции и как они работают, мы разберем чуть позже — сейчас о порядке выполнения программы:

Как только компьютер подключается к питанию, его надо поставить на паузу через специальную кнопку на плане тактового процессора.

Оперативная память заполняется вручную через DIP-переключатели, связанные с чипами SN74LS173, о которых рассказывалось выше.

Пауза отжимается и компьютер выполняет инструкцию из ячейки памяти по адресу 0000, потом инструкцию 0001, 0002 и так далее.

Что такое генератор тактовых импульсов?

Человечество на современном этапе не может обойтись без использования цифровых технологий. Компьютеры, телевизоры, мобильные телефоны, фотоаппараты, часы и многочисленные иные гаджеты, которые стали так привычны и незаменимы, имеют в своей основе электронные компоненты, одной из важнейших характеристик функционирования которых является тактовая частота. Это последовательность импульсов (обычно прямоугольной формы), которая определяет порядок и скорость выполнения операций устройства.

Работа тактового генератора основана на принципе самовозбуждения электронной схемы, охваченной петлёй положительной обратной связи. Технические решения конструкционно могут быть самыми разными: применяются транзисторы (как правило, в составе специализированных чипов), туннельные диоды и иные компоненты с нелинейными вольт-амперными характеристиками. Обычный приём разработчиков аппаратуры на цифровых интегральных микросхемах – использование нескольких инверторов, соединённых последовательно, а для создания сдвига фаз и настройки периода колебания служит RC-цепочка.

Роль тактового генератора

Для взаимодействия различных узлов цифровых устройств необходима синхронизирующая привязка к единому циклическому процессу. Считая количество тактов эталонной частоты, можно отмерять временные интервалы и управлять моментами начала той или иной операции. Базовый генератор определяет частоту функционирования центрального процессора. На ней же основывается алгоритм работы шин компьютера (PCI, SATA, оперативной памяти).

Для понижения частоты в два раза, достаточно одного триггера. Если же их несколько, из них, комбинируя связи, можно организовать счётчик с заданным коэффициентом деления. Так формируются импульсы с определёнными временными параметрами, по фронту или спаду которых срабатывают те или иные узлы процессора и оперативной памяти. Отработка элементарной инструкции в зависимости от её типа может занимать от одного до нескольких десятков тактов. Таким образом, от выбора тактовой частоты напрямую зависит быстродействие компьютера.

Важность стабильности параметров генератора

Самый простой пример: сотовый телефон связывается с базовой станцией на строго определённой частоте. Идентификация абонента происходит с помощью передачи индивидуального кода, присвоенного sim-карте (Subscriber Identification Module). При малейшем изменении периода колебаний задающего генератора мобильного телефона может произойти сбой, и установление связи между абонентами станет невозможным. Поэтому для стабилизации частоты используют кварцевый генератор – именно этот компонент обладает необходимыми свойствами.

25. Тактовый генератор

Тактовый генератор имеет в своем составе низкочастотный RC-генератор, Основной тактовый генератор и модуль ФАПЧ (PLL). Он вырабатывает следующие тактовые сигналы:

Интерфейс тактового генератора встроен в контроллер управления потребляемой мощности PMC и описан в главе 26.9. Однако имена регистров тактового генератора объединены в группе CKGR_.

25.2 Низкочастотный RC генератор

25.3 Основной тактовый генератор

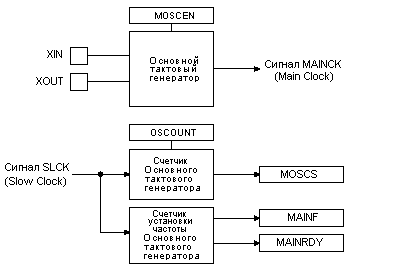

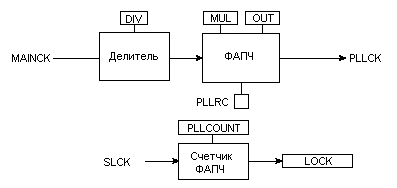

Рис. 25-1. Структурная схема тактового генератора

25.3.1 Включение основного тактового генератора

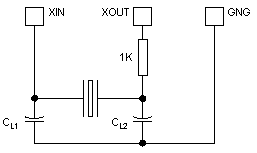

Тактовый генератор включает в себя основной тактовый генератор, работающий с кварцевым резонатором частотой от 3 до 20 МГц. Типовая схема включения кварца приведена на рис.25-2. При работе с кварцем на частотах до 8 МГц требуется установка резистора номиналом 1 кОм. К выводам XIN и XOUT подключаются конденсаторы емкостью по 25 пФ. Следовательно, емкости CL1 и CL2 можно не устанавливать, при использовании кварца с входной емкостью равной 12,5 пФ. Более подробная информация по электрическим характеристикам приведена в секции характеристик по постоянному току.

Рис. 25-2. Типовая схема включения кварцевого резонатора

25.3.2 Время запуска основного тактового генератора

Время запуска основного тактового генератора приведено в секции характеристик по постоянному току. Время запуска зависит от частоты кварца и уменьшается с ростом частоты.

25.3.3 Управление основным тактовым генератором

Для уменьшения потребления мощности при запуске системы основной тактовый генератор отключен, при этом выбран низкочастотный RC генератор.

Программно возможно включить/отключить основной тактовый генератор для уменьшения потребляемой мощности. Для этого производится сброс MOSCEN бита в регистре основного генератора (CKGR_MOR).

Отключение основного тактового генератора сбросом MOSCEN бита в CKGR_MOR приводит к автоматическому сбросу MOSCS бита в регистре PMC_SR, сообщая, что основной тактовый генератор отключен.

При разрешенном основном генераторе, пользователь должен инициализировать счетчик основного генератора значением, соответствующим времени запуска генератора. Время запуска зависит от частоты подключенного кварца.

После записи MOSCEN бита и значения OSCOUNT в регистр CKGR_MOR для разрешения основного генератора, MOSCS бит в регистре статуса PMC_SR сбрасывается. Счетчик начинает отсчет на убывание от значения OSCOUNT с частотой сигнала в 8 раз меньшей частоты сигнала SLCK. Так как значение OSCOUNT кодируется 8-ю битами, то максимальное время старта составляет примерно 62 мс.

При достижении счетчиком нуля, MOSCS устанавливается, сообщая, что частота основного генератора установилась. Установка MOSCS бита в PMC_IMR может быт источником прерывания для процессора.

25.3.4 Счетчик установки частоты основного генератора

Счетчик установки частоты основного генератора позволяет точно определить частоту подключенного кварцевого резонатора. Это может быть полезно для программы бут загрузчика для конфигурации микроконтроллера правильным значением тактового сигнала, независимо от приложения.

Счетчик установки частоты основного генератора начинает счет на скорости основного тактового генератора после появления положительного фронта низкочастотного генератора (сигнала SLCK), после стабилизации основного тактового генератора, то есть, как только установлен MOSCS бит. Затем по 16-ому отрицательному фронту сигнала SLCK устанавливается MAINRDY бит в регистре основной тактовой частоты CKGR_MCFR (Main Clock Frequency Register) и счетчик останавливает счет. Это значение может быть считано в поле MAINF регистра CKGR_MCFR и равно числу циклов основного тактового генератора за 16 периодов сигнала SLCK. Таким образом, может быть определена частота подключенного кварцевого резонатора.

25.3.5 Подключение внешнего генератора

Вместо подключения кварца к контроллеру можно подключить внешний генератор. В этом случае внешний тактовый сигнал подается на вывод XIN. Входные характеристики вывода XIN в этих условиях приведены в секции электрических характеристик. Программист должен не забыть установить OSCBYPASS бит в 1, а MOSCEN бит в 0 в регистре основного генератора CKGR_MOR (Main OSC Register) для правильной работы с внешним тактовым сигналом.

25.4 ФАПЧ и Делитель частоты

ФАПЧ включена во входной делитель для увеличения точности результирующего тактового сигнала. Тем не менее, пользователь должен выбрать минимальное значение частоты на входе ФАПЧ при программировании делителя.

На рис.25-3. приведена структурная схема ФАПЧ и Делителя частоты.

Рис. 25-3. Структурная схема ФАПЧ и Делителя частоты

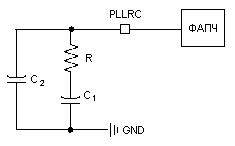

Схема ФАПЧ требует подключения внешнего фильтра 2-го порядка через вывод PLLRC. На рис.25-4 приведена схема такого фильтра.

Рис. 25-4. Схема фильтра для ФАПЧ

25.4.2 Программирование схемы ФАПЧ и Делителя частоты

Делитель может быть установлен в диапазоне от 1 до 255. При записи в поле делителя DIV нуля, на выходах соответствующего делителя и ФАПЧ устанавливается сигнал низкого уровня. После сброса, в каждое поле DIV записывается нуль, что приводит к установке нуля на соответствующих тактовых входах ФАПЧ.

Схема ФАПЧ допускает умножение сигналов с выходов делителей. Частота тактового сигнала ФАПЧ зависит от частоты исходного сигнала и параметров DIV и MUL. Значение выходной частоты определяется выражением (MUL + 1)/DIV. Запись в поле MUL нуля приводит к отключению ФАПЧ. Включение схемы ФАПЧ осуществляется записью в поле MUL значения большего нуля.

После включения ФАПЧ или изменения одного из ее параметров LOCK бит в регистре PMC_SR автоматически сбрасывается. Значения, записанные в поле PLLCOUNT в регистре CKGR_PLLR, загружаются в счетчик ФАПЧ. Счетчик ФАПЧ после этого декрементируется на скорости сигнала SLCK до достижения нуля. В этот момент LOCK бит в регистре PMC_SR установлен и может сформировать прерывание для процессора. Пользователь должен загрузить число тактов сигнала SLCK в поле PLLCOUNT, что определяет время перекрытия переходного процесса ФАПЧ. Длительность переходного процесса зависит от фильтра ФАПЧ. Начальные параметры ФАПЧ и выходная частота могут быть вычислены с использованием специальной утилиты предоставляемой фирмой Atmel.